Without advanced packaged and integrated chips, we can't live in smart houses, drive autonomous cars or communicate through 5G networks. Future societal challenges in energy, healthcare, mobility, agriculture and food mean that an increasing degree of intelligence must be built into products and services. As a key enabling technology, chips and their packages make this intelligence possible.

#### Solutions to societal challenges

Chip Integration Technology Center (CITC) is a non-profit, joint innovation center specializing in heterogeneous integration and advanced chip packaging technology. We bring leading innovations in chip integration and packaging technology to market in a selected and growing number of application areas. As such, we provide solutions to societal challenges: integration for tomorrow.

#### Innovation meets collaboration

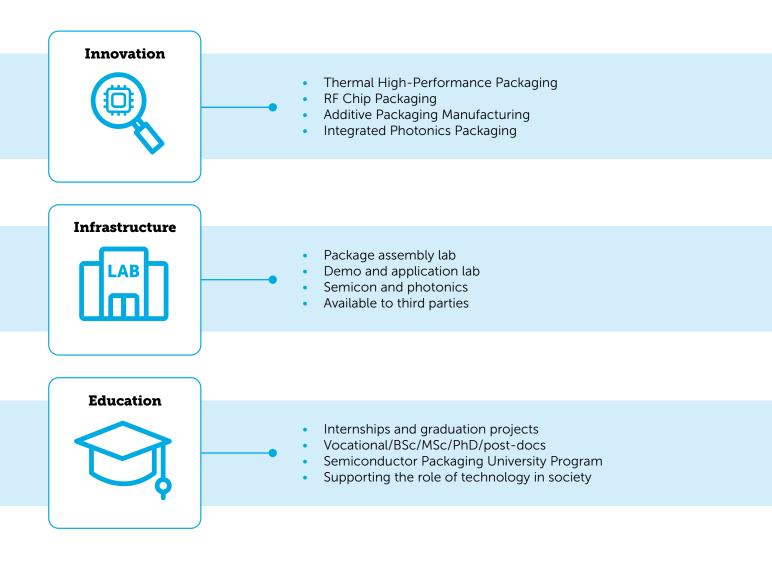

Evolving chip technology is not a one-man business. Collaboration is vitally important in innovation. CITC has created an effective ecosystem in which companies, research and educational institutes work on bridging the gap between academics and industry. Together, we work on a new generation of packages providing smart, safe and rugged housing for chips. CITC's contribution to the ecosystem is to provide access to innovation, infrastructure and education.

### **Access to innovation**

CITC runs its research programs in close collaboration with partners and customers. We therefore work together with device manufacturers, equipment manufacturers, material suppliers and system integrators in pre-competitive joint innovation programs. Our research efforts are focused on four program lines.

# Program line 1: Thermal High-Performance Packaging

The transition to Wide-Band-Gap for many applications has increased the power generation by semiconductor devices. In combination with miniaturization, this results in higher die temperature and higher thermomechanical stresses. To address these technological challenges, our Thermal High-Performance program concentrates on developing novel thermo-mechanical design strategies and device platforms focusing on Ag-sinter die-attach and Cu lead frames. These platforms are composed of low-stress and high-reliability rugged interconnect solutions and molds with high power dissipation capability.

Our approach for finding rugged die-attach solutions is powered by our key competences:

- Assembly and integration

- Thermomechanical modeling and simulations

- Reliability and testing

- In-situ failure detection and monitoring

### Program line 2: RF Chip Packaging

CITC's RF Chip Packaging program is developing technologies to enable the next generation mm-Wave applications such as 6G and automotive radar. Our focus is on Antenna in Package (AiP) architectures, where the antenna system is integrated in the package.

In our approach, we combine co-design methodologies and prediction models, expertise on packaging manufacturing technologies and materials. We have developed multidisciplinary competence and a state-of-the-art packaging infrastructure, including:

- Characterization methods for dielectric properties of packaging materials

- RF and antenna design and simulations

- Thermomechanical modelling

- Fully equipped back-end assembly and integration capability for building proof-of-concept packages and clean room processing for advanced packaging processes

- Additive manufacturing technologies for RF packaging applications

## **Program line 3: Additive Packaging Manufacturing**

Digital or additive manufacturing (AM) is a potential disruptive technology for the semiconductor packaging industry. Because it is currently reaching a tipping point in usability, AM creates opportunities for newpackaging concepts with increased design freedom and reduced manufacturing complexity. Our Additive Packaging Manufacturing program focuses on applications that cannot be realized using traditional manufacturing technologies.

In collaboration with material and equipment companies, we build prototypes to evaluate and develop new industrial solutions. Application areas include:

- Power electronics

- RF, 3D antenna structures, acoustic sensors and transducers

- Pressure sensors

- Micro-fluidic devices

- Heterogeneous integration of components and chips in complex systems or subsystems

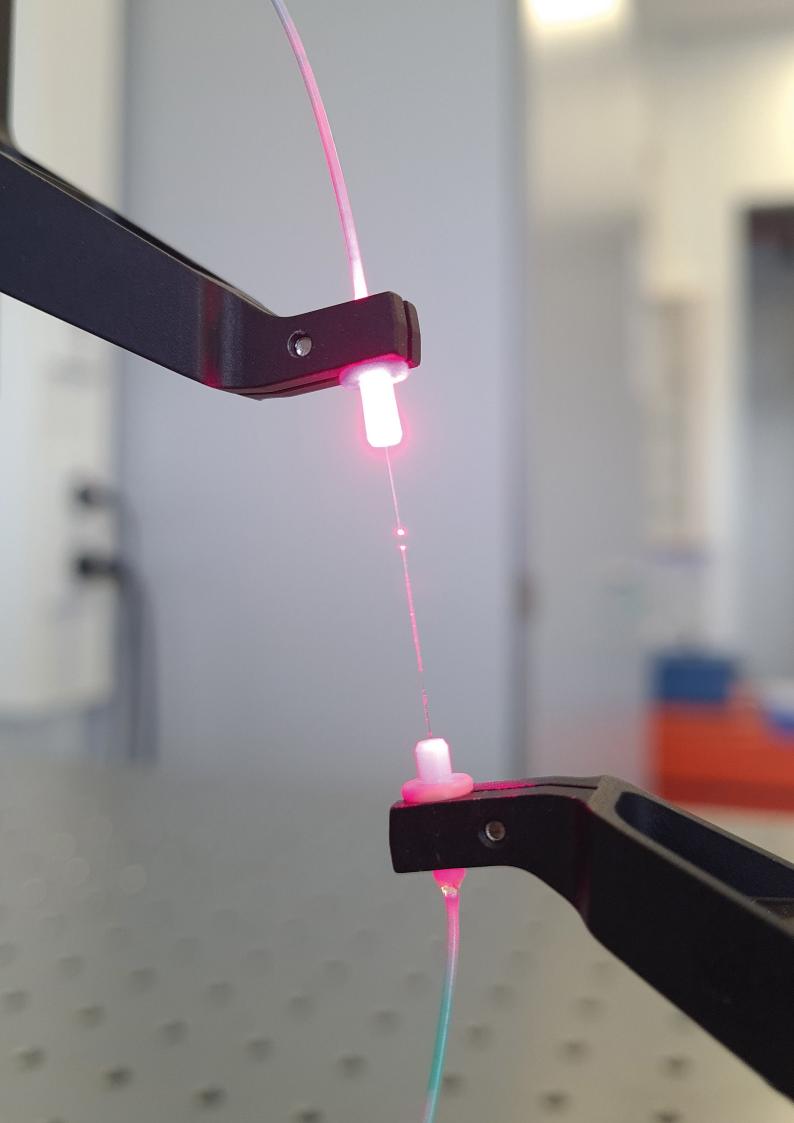

## **Program line 4: Integrated Photonics Packaging**

Photonic Integrated Circuits (PICs) are becoming the dominant technology in datacom and telecom. In our Integrated Photonics Packaging program, we develop new packaging concepts in close cooperation with the customer.

CITC is part of the PODIUM consortium that combines the electrical and optical packaging know-how of its partners to accelerate assembly process development and provide an efficient path to volume production.

We use our expertise in high-power electronics packaging and RF packaging in our photonic packaging development to address topics like:

- Thermal management

- High I/O chip-to-chip interconnect

- Chip-to-chip alignment reliability

- Integration of photonics with microelectronics

#### **Access to infrastructure**

CITC's lab facilities support the innovation programs and contribute to education through internships and MSc/PhD programs. Additionally, our lab serves as demo and application lab for new types of equipment and materials. The lab is available to third parties to enable them to develop, test and implement new packaging solutions.

#### In-house assembly processes and technical capabilities

Our lab has all the equipment and tooling for basic packaging assembly technologies:

- Surface (plasma) cleaning/sample preparation

- Dispensing/glue-solder depositing; dispensing, dam and fill, potting

- Die bonding; glue-solder-sinter

- Wire bonding; wedge-wedge, ball-wedge, Cu, Al

- Optical assembly; active, passive

- Testing; thermal, cross-sectioning, x-ray

This equipment allows us to examine the physical aspects of various assembly processes, with the ability to perform fast prototyping for proof-of-principle samples using industrial quality samples. CITC also has the equipment to test and evaluate the quality of the assembly process.

#### Additional external facilities

Besides our own lab facilities, we have access to the lab facilities of our strategic partners TNO and Delft University of Technology (TUD), primarily for wafer-level processes. This includes the facilities of TNO Holst Centre in Eindhoven and the Else Kooi Lab of TUD. For specific research, we can also use the labs of our partners Sencio, EPR and Eindhoven University of Technology (TUe).

### **Access to education**

Education and training are key to securing the future of the semiconductor industry in Europe. In close cooperation with companies and educational institutes, CITC organizes targeted education and training for young talent. By providing a connection between education and industry, we contribute to the training and skills of people who match industry needs.

## Internships and PhD research

CITC holds an Accredited Work Placement Company qualification that enables us to train secondary vocational education students in professional practice.

With our close ties to educational institutes like Radboud University, Delft University of Technology, Eindhoven University of Technology, University of Twente and HAN University of Applied Sciences, we regularly offer internships, graduation assignments and PhD projects to students.

### **Semiconductor Packaging University Program**

At the same time, we support lifelong learning by enabling semiconductor staff to stay up to date with the latest developments in the industry. Together with HAN University of Applied Sciences, we developed the Semiconductor Packaging University Program. The program is offered as a minor to students and focuses on the design and manufacturing of semiconductor packages. It includes practical assignments that are completed on the premises of CITC and several semiconductor companies in our network.